# BYU NASATMR RISC-V IDAHO MCU for CWS

ECEN 499 – Senior Project

Zac Carico, James Thomas, Sam Bagley, Maxwell Bakes, Michael Ashford

## Objective

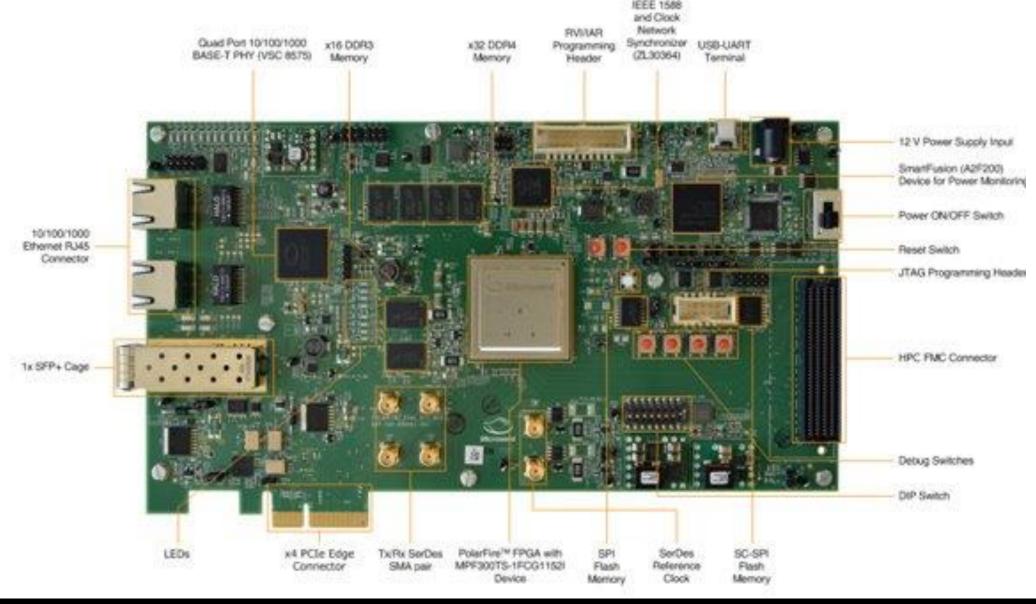

Using the PolarFire FPGA Eval kit and a custom PCB, benchmark various RISC-V core configurations in Triple Modular Redundancy (TMR) for use in NASA's Caution and Warning System (CWS) in the Portable Life Support System (PLSS) of the newest space suit (xEMU).

## Hardware and Software

- PolarFire FPGA

- Libero

- SoftConsole

- Altium

## **Triple Modular Redundancy**

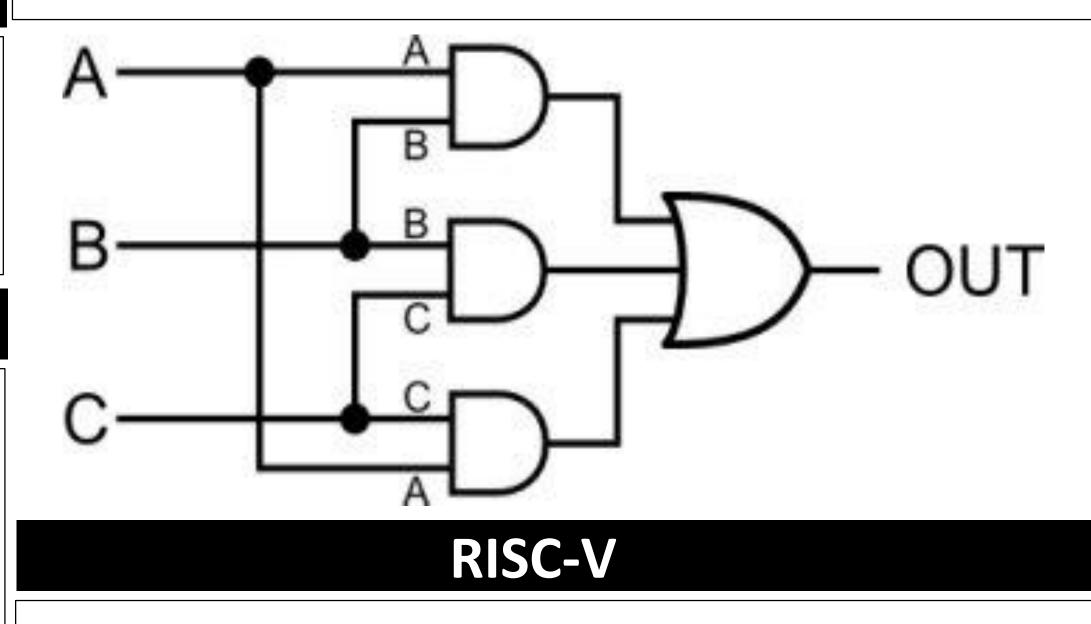

Radiation causes bit flipping in electronic applications and

## Conclusions

space is full of radiation that will cause errors, especially in a large project such as a processor. The PolarFire FPGA is radiation hardened, while significantly reduces the number of bit flips, but it's not a perfect protection. We implement a tool called Triple Modular Redundancy to error check ourselves. Input data is sent to three identical circuits and then voted on, as seen in the schematic below. We have three full-featured RISC-V cores on our FPGA. After each cycle, our voting circuitry checks to make sure all three cores have the same results. The voting circuits are then error checked for bit flips.

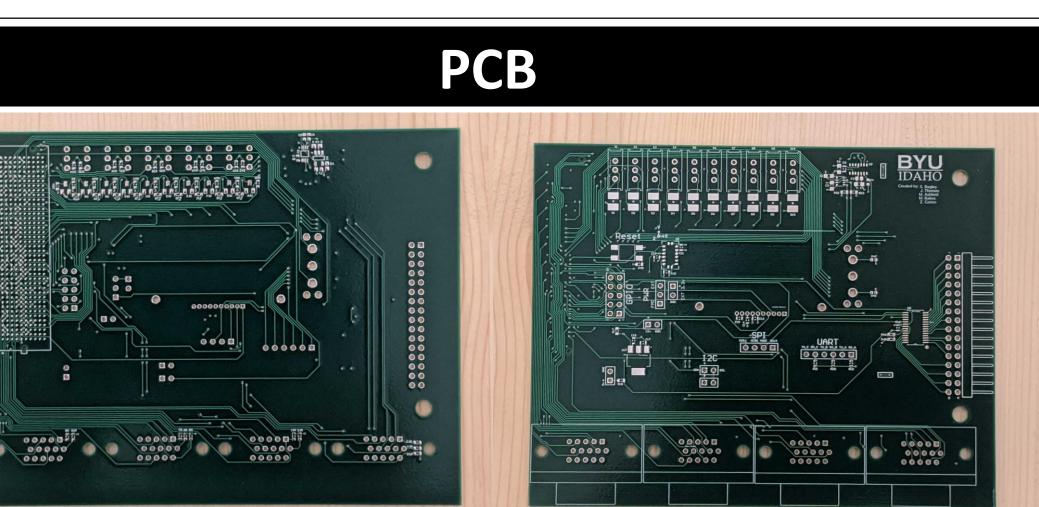

We created a base RISC-V processor in TMR with an addition of beginning 3 other cores. Created modules for SPI, I2C, UART, and GPIO. Began a Module for LVDS UART. Created a PCB to test the FPGA

#### **Future Developments**

- •Finish the other three processor designs.

- •Fix memory controller compatibility issues between AHB processors and AXI memory.

**RISC-V** is an open source Instruction Set Architecture developed by UC Berkeley with funding by Microsoft and Intel. It is very modular, as you can use three word-widths, 32, 64, and 128 bits. It has features to improve speed, while also being power and cost efficient. It is finding increasing popularity in the world of electronics as you can create small, fast, or energy efficient processors based off the same architecture.

Finish the LVDS UART

•Fully test SPI, I2C, GPIO, and LVDS UART

- •Place and solder all components using the solder mask, solder paste, and a reflow oven

- •Use probe to test the connections and inspect solder joints